臺(tái)積電從原來的晶圓制造代工角色,逐步跨界至封測(cè)代工領(lǐng)域(InFO、CoWoS及SoIC等封裝技術(shù)),試圖完整實(shí)體半導(dǎo)體的制作流程。

根據(jù)不同產(chǎn)品類別,臺(tái)積電的封測(cè)技術(shù)發(fā)展也將隨之進(jìn)行調(diào)整,如同HPC(High Performance Computer)高效能運(yùn)算電腦將以InFO-oS進(jìn)行封裝,服務(wù)器及存儲(chǔ)器部分選用InFO-MS為主要封裝技術(shù),而5G通訊封裝方面即由InFO-AiP技術(shù)為主流。

透過上述不同封裝能力,臺(tái)積電除本身高品質(zhì)的晶圓制造代工能力外,更藉由多元的后段制程技術(shù),滿足不同客戶的產(chǎn)品應(yīng)用需求。

臺(tái)積電積極發(fā)展封測(cè)技術(shù)如InFO-AiP,有效縮減元件體積并強(qiáng)化產(chǎn)品功能

面對(duì)AI、5G通訊時(shí)代逐步來臨,臺(tái)積電作為晶圓制造的龍頭廠商,除了鉆研更精密的線寬微縮技術(shù)外(由現(xiàn)行7納米制程,逐步演進(jìn)至5納米,甚至3納米制程條件),封測(cè)代工領(lǐng)域也是另一項(xiàng)發(fā)展重點(diǎn)指標(biāo)。透過前述相關(guān)封測(cè)技術(shù)(如InFO-oS、InFO-MS及InFO-AiP等)的開發(fā),臺(tái)積電試圖整合元件制造與封裝能力,藉此提供客戶較完整的實(shí)體半導(dǎo)體之制作流程及服務(wù),以滿足各類高端產(chǎn)品輕、薄、短、小的使用目標(biāo)。

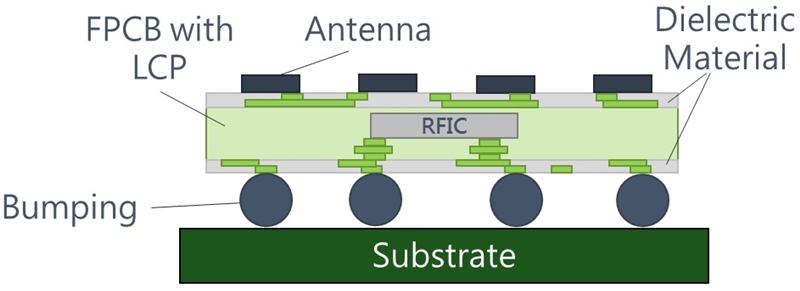

值得一提,臺(tái)積電在5G通訊領(lǐng)域中主打的InFO-AiP(Integrated Fan-out Antenna in Package)封裝技術(shù),于后續(xù)即將開展的毫米波(mm-Wave)通訊時(shí)程,也將扮演極重要角色。如同前述,結(jié)合臺(tái)積電本身先進(jìn)半導(dǎo)體制造能力,使線寬精細(xì)度得以提高外,再搭配自身研發(fā)的獨(dú)門封裝技術(shù)InFO-AiP,將驅(qū)使整體元件體積有效縮減10%,并且強(qiáng)化天線訊號(hào)增益四成成效。

▲臺(tái)積電之InFO-AiP結(jié)構(gòu)示意圖。(Source:拓墣產(chǎn)業(yè)研究院整理,2020.2)

不同于封測(cè)代工廠商,臺(tái)積電發(fā)展策略仍以晶圓制造為主、封測(cè)代工為輔

考量臺(tái)積電對(duì)5G毫米波AiP封裝技術(shù)之積極搶市態(tài)度,對(duì)現(xiàn)行封測(cè)代工廠(如日月光、Amkor、江蘇長電及矽品等)而言,發(fā)展策略已產(chǎn)生不小的競(jìng)爭壓力。假若設(shè)想于技術(shù)研發(fā)為企業(yè)發(fā)展及策略重點(diǎn)時(shí),則臺(tái)積電于封裝策略的開發(fā)進(jìn)程,將有別于其他封測(cè)代工廠商的政策目標(biāo)。

由于臺(tái)積電的主力強(qiáng)項(xiàng)為高精密晶圓制造代工,將能提供客戶復(fù)雜且整合度較高的半導(dǎo)體制造服務(wù),藉此因應(yīng)如AI及通訊元件等高階產(chǎn)品的市場(chǎng)需求;然而只專精于半導(dǎo)體晶圓制造代工,對(duì)龍頭廠商的發(fā)展性而言似乎略顯不足。依現(xiàn)行發(fā)展脈絡(luò),臺(tái)積電除了高端晶圓制造外,更進(jìn)一步搭配自身開發(fā)的封裝技術(shù),以延續(xù)元件制造中線寬微縮的目標(biāo)趨勢(shì),使封裝中的重分布層(RDL)金屬線路,能透過較精細(xì)的制作方式,進(jìn)行后段的堆疊程序,最終達(dá)到有效降低元件體積,并提高產(chǎn)品的功能性。

臺(tái)積電對(duì)半導(dǎo)體的發(fā)展策略,仍以晶圓制造為主、封測(cè)代工為輔,目前將重心擺在自身高端晶圓制造代工能力,搭配相關(guān)先進(jìn)封測(cè)技術(shù)開發(fā),期望完整實(shí)體半導(dǎo)體的制作流程。